SMIC is the fab that Huawei contracts to make the Kirin 9000S. Huawei has the capability to make most other chips itself just not mobile phone SOCs.

SMIC is the fab that Huawei contracts to make the Kirin 9000S. Huawei has the capability to make most other chips itself just not mobile phone SOCs.

AMD always having the process advantage over Intel and Nvidia but still ending up as the underdog is puzzling.

AMD Zen 2 on 7nm should’ve destroyed Comet lake on 14nm but it didn’t. Rocket Lake faired a lot worse against Zen 3 but it was an iffy 10nm to 14nm port job.

AMD Navi GPUs on 7nm somehow were less efficient than Nvidia’s Turing on 12nm(16nm+) while also not having ray tracing or tensor cores. Nvidia were left cocky enough to go for Samsung’s discount 8nm the gen after instead of attaining process parity.

It’s going to get worse because the gains from each succeeding node diminishes so AMD can no longer count on the gains to make them competitive.

It doesn’t help that Qualcomm’s 888, and 8 Gen 1 were a disappointment. Even more so since they were the debut of ARM’s Cortex-X series of performance cores. Those were supposed to be ARM’s attempt at matching Apple’s custom cores. Thermal throttling issues meant that they weren’t even real upgrades from the 865 in terms of sustained performance.

The original Kirin 9000 was from 2020. Hard to improve performance, if the US government is doing everything to hinder your ability to make chips in the first place. Huawei matching the original TSMC 5nm EUV chip with just SMIC 7nm DUV is a miracle.

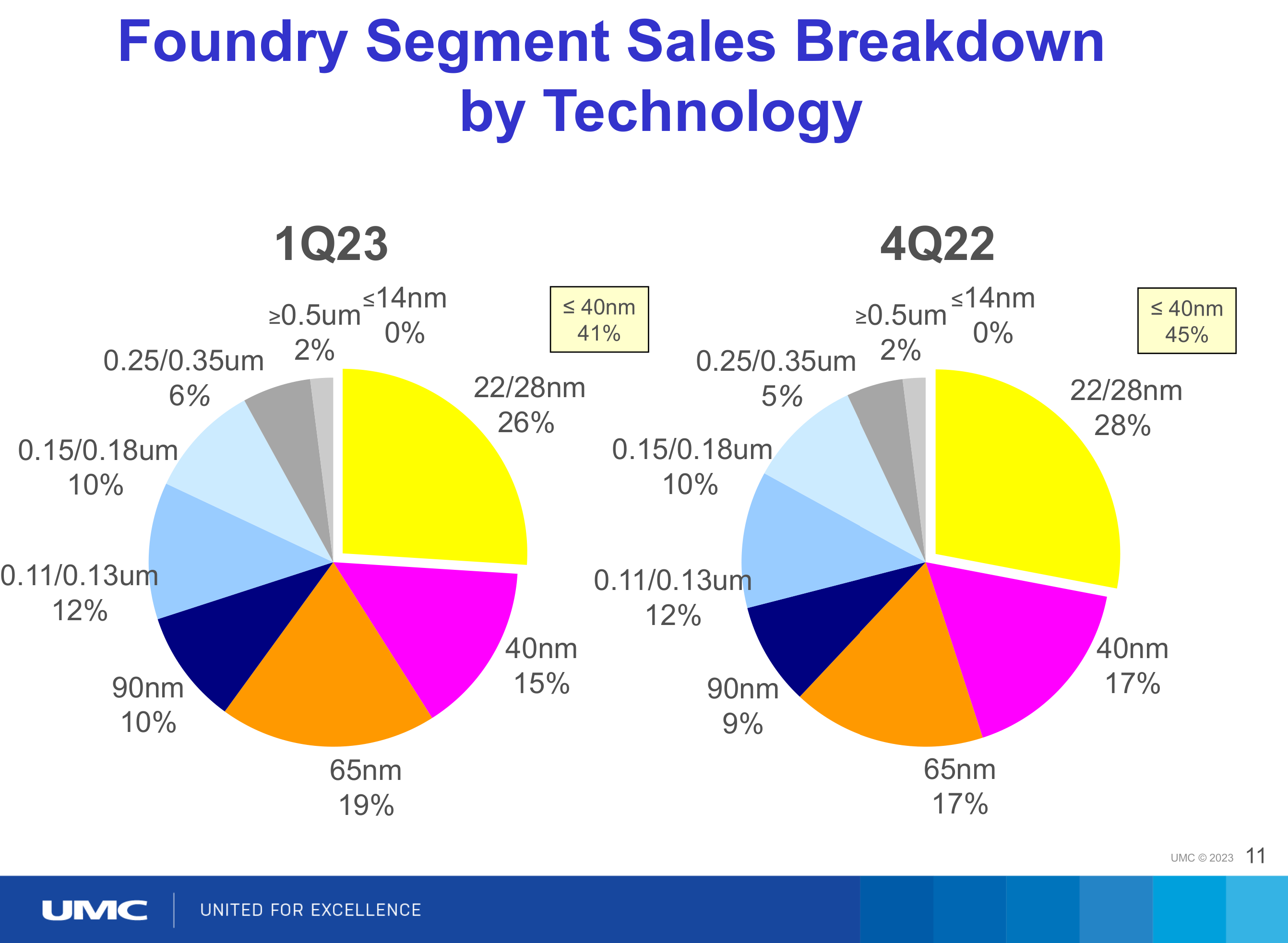

Well look at the other contract fabs that could buy EUV scanners if they wanted to.

GlobalFoundries gave up on 7nm so 14/12nm is the best they have. UMC barely makes any 14nm chips so they definitely aren’t pursuing anything below 7nm. Getting to 7nm is an investment few can make and it won’t pay off for most. The number of fabless chip companies that can afford to design for <7nm and need the leading edge in performance is tiny. A high price of entry to serve so few customers.

SMIC is only the third pure play contract fab to offer <=7nm and Samsung needed EUV to get to 7nm unlike SMIC and TSMC.

Judging by the performance and density of the Kirin 9000S, SMIC’s 7nm DUV is at least as good as Samsung’s 5nm EUV. The same A510 cores made with SMIC’s 7nm are as efficient if not more so than those made with Samsung 4nm.

The previous top Huawei phone, the P60 Pro has the 4G variant of the 8+ Gen 1, which was made with TSMC 4nm. The Mate 60 Pro being technically a downgrade in process node is something few if any of its users will actually notice in practice. Huawei could’ve easily just made a 5G modem and paired it with an 8 Gen 2. It would’ve been a lot easier to make a tiny modem yield but they chose the harder option of making an entire SOC. They succeeded in matching if not surpassing the TSMC 5nm made original that stopped being made on September 15, 2020. All the sanctions could do was delay further production of the Kirin 9000 for 3 years.

I don’t think the CPU performance is down to optimization. The 4 custom Taishan performance cores having hyper threading is probably why. The Kirin 9000S has 8 cores / 12 threads, which is why the multi-core score is so high.

The GPU drivers definitely aren’t ready yet; it can’t render Genshin Impact correctly. It’s not an ARM Mali reference design; it’s Huawei own Maleoon 910. The only things from ARM are the Cortex-A510 efficiency cores, and the instruction set.

The Kirin 9000S is only 2% larger than the original 9000, which was made using TSMC 5nm. It performs far better than any 7nm chip.

CPU Performance almost matches the 4nm Exynos 2200, which because the 2300 was a no show is the best chip Samsung has.

GPU Performance although not a match for the original 9000 still exceeds the 5nm Snapdragon 888.

Geek Bench 5 Multi/Single core Scores

28nm is the nominal resolution of the scanner. The chips that can be made with a single exposure. In that measure no ASML DUV scanner is 7nm either. The physics of 193nm light makes it impossible for any DUV scanner to have a nominal resolution of 7nm. 7nm chips are made using DUV by exposing 4 times at a 28nm resolution. The same quad patterning techniques allows 22nm chips to be made with a 90nm machine.

The name is also misleading 7nm chips aren’t sub 9nm. TSMC’s 7nm chips are physically 10nm. The marketing names haven’t matched for years. It all started when TSMC sold 20nm FinFET under 16nm branding as they believed the addition of FinFET gave it 16nm performance. Then the entire industry adjusted their naming conventions to match with TSMC.

SMIC, Huawei didn’t get to where they are by compromising. They never would’ve bought the Chinese domestic alternatives if not for sanctions. Price doesn’t matter in this industry, what they’re looking for is the best in the market. This is not the type of capital equipment that subsidies can sell. Which is why when US scanner manufacturers couldn’t compete with ASML, they completely failed as economically viable businesses and their assets were sold off.

China prepared for this 17 years ago. They launched the “02 Special Project” all the way back in 2006. The companies established by those grants have existed years before the sanctions. They were able to develop the products but selling them was another thing entirely, until the sanctions hit causing a massive boom in their revenue. People forget that it was market conditions that killed GlobalFoundries 7nm effort not technical issues. The same reason UMC gave up on anything more advanced than 14nm. Sanctions created the inevitability of Chinese 7nm by wedding the world’s largest telecom equipment vendor, Huawei to SMIC.

It’s an amusing coincidence that by the time ASML will no longer be granted export licenses for their 5nm capable DUV scanners, the NXT:2000i and above, SMEE will be selling a 7nm capable scanner, the SSA/800-10W. A machine easily comparable to the NXT:1980Di that TSMC used to develop their N7 process. The fact that the NXT:1980Di and anything less advanced than it isn’t going to be export restricted is an implicit acknowledgement of the Chinese capability of making competing machines.

5nm capable DUV scanners, such as the SSA/900 still in development, might be a requirement for SMIC N+2 however as the “7nm” Kirin 9000S is only 2% larger than the TSMC N5 made Kirin 9000. That suggest a density far exceeding anything any other foundry has been capable of with just DUV, such as Intel 7 or TSMC N7/N7P.

Applied Materials and LAM are less of an issue. AMEC has been selling 5nm etching systems to Samsung and TSMC for years.

TSMC made Kirin 9000 ran out in 2021, P50 Pro was the last phone to use it and the Kirin 820 ran out in 2022. It’s only the 5G base stations that still use TSMC made HiSilicon chips.

That’s based on TSMC’s own test chip not an actual customer’s. 17.92 mm² is incredibly tiny when SoCs, CPUs and GPUs range in size from 100 to 600 mm² increasing the proportion of chips with defects as the number of chips on the wafer drops.

From that very article

In that case, let us take the 100 mm2 die as an example of the first mobile processors coming out of TSMC’s process. Again, taking the die as square, a defect rate of 1.271 per cm2 would afford a yield of 32.0%.

As TSMC themselves designed the chip, they definitely followed all their design rules for that process to maximize yield. No customer would do that.

Anand explains this in one of his articles.

But have no fear. What normally happens is your foundry company will come to you with a list of design rules and hints. If you follow all of the guidelines, the foundry will guarantee that they can produce your chip and that it will work. In other words, do what we tell you to do, and your chip will yield.

The problem is that if you follow every last one of these design rules and hints your chip won’t be any faster than it was on the older manufacturing process. Your yield will be about the same but your cost will be higher since you’ll bloat your design taking into account these “hints”.

Generally between process nodes the size of the wafer doesn’t change. We were at 200mm wafers for a while and now modern fabs use 300mm wafers. The transistor size does shrink however, so in theory you could fit more die on a wafer with each process shrink.

The problem is with any new process, the cost per wafer goes up. It’s a new process, most likely more complex, and thus the wafer cost is higher. If the wafer costs are 50% higher, then you need to fit at least 50% more die on each wafer in order to break even with your costs on the old process. In reality you actually need to fit more than 50% die per wafer on the new process because yields usually suck at the start. But if you follow the foundry’s guidelines to guarantee yield, you won’t even be close to breaking even.

The end result is you get zero benefit from moving to the new process. That’s not an option for anyone looking to actually use Moore’s Law to their advantage. Definitely not for a GPU company.

The solution is to have some very smart people in your company that can take these design rules and hints the foundry provides, and figure out which ones can be ignored, and ways to work around the others. This is an area where ATI and NVIDIA differ greatly.

TSMC N7, N7P and Intel 7 don’t use EUV. It’s all quad patterned DUV. DUV lithography has been in use since the 1990s going from 800nm to N7P.

Every single node after TSMC’s so called 16nm has been all marketing. It would’ve more accurate to call TSMC 16FF as 20nm FinFET. This is why Intel brands what they themselves called 10nm as Intel 7 to bring their marketing more in line with TSMC’s.

SMIC N+1 has a density of 89 million of transistors per mm² while TSMC N7 has 91.2. TSMC 10FF and Samsung 10LPP only offer slightly more than half that density.

Neoliberals will do anything to downplay or outright deny any historical incident where import substitution lead to industrialization. Creating captive markets for the dumping of manufactured products was one of the prime drivers of colonialism, which continued under neocolonialism. With sanctions, the US is unintentionally undermining their own hegemony. Businesses like having access to markets and moats. They are giving moats to one side and stripping access to the other.

Sanctions will do for Chinese chip makers what the great firewall did for Chinese internet giants.

Seeing /u/dylan522p acknowledge reality somewhat is refreshing although the conclusion is the predictable “Washington is just sanctioning wrong, if they followed my foolproof sanction regime it would magically work”. Liberals attacking him for this article is quite hilarious. They’re really intolerant of even the slightest deviation from US state department rhetoric.